技術文章分析 | 突破 100GHz 瓶頸:GPU 叢集 400G/lane EML 與先進封裝技術

- 2天前

- 讀畢需時 5 分鐘

各位光通訊與半導體業界的夥伴們,歡迎來到 STT 深度解析。最近 AI 算力基礎設施的需求簡直像坐火箭,像 GPT-4 這種具備上兆參數的大型語言模型,讓 GPU 叢集內部的資料傳輸壓力來到史無前例的高峰。為了平行化這些龐大的 GPU 機架,業界正積極轉向更高速的光纖互連與可插拔收發器。

我們都知道,要邁向下一代 3.2 Tbps 可插拔模組,或是因應 GTC 大會上備受矚目的高密度 CPO (Co-Packaged Optics) 交換器架構,單通道 400 Gbps (400G/lane) 已經是無法妥協的硬指標。這意味著光調變器的頻寬必須突破 100 GHz 的天險。今天要解析的這篇來自三菱電機 (Mitsubishi Electric) 的最新力作,不僅在 EML 晶片結構上動刀,更直接挑戰了限制頻寬的元凶——「打線封裝 (Wire bonding)」,提出專為高密度邊緣光學設計的混合基板與無打線技術。這篇研究完美切中當前產業從 1.6T 跨向 3.2T 的痛點,非常值得我們細細拆解。

參考來源

論文標題: High-Speed EML and Assembly Techniques for GPU Cluster System

作者: M. Shirao, T. Fujita, Asami Uchiyama, Shinya Okuda, T. Nagamine, Kenichi Abe, and N. Ohata

發表單位: Mitsubishi Electric Corporation (三菱電機)

發表平台: JOURNAL OF LIGHTWAVE TECHNOLOGY, VOL. 44, NO. 3, FEBRUARY 1 2026 (Invited Paper)

深度圖表分析:從晶片微縮到混合基板的技術突圍

這篇論文的論述邏輯非常清晰:先優化 EML 晶片本身的電容,接著解決打線造成的寄生電感,最後針對 CPO 應用提出無打線的 3D/2.5D 封裝方案。我們逐圖來看這些精采的實驗數據:

第一階段:EML 晶片高台地結構與寬度微縮 (Fig. 1 - Fig. 3)

Fig. 1 (EML 結構設計): 這裡展示了結合 DFB 雷射、電吸收調變器 (EAM) 以及光斑尺寸轉換器 (SSC) 的 EML 結構。 最關鍵的是 EAM 採用了「高台地 (High-mesa)」結構,並在台地兩側填充低折射率的絕緣材料。這讓研究團隊能在縮小台地寬度(降低電容)的同時,依然把光場緊緊鎖在吸收層內,維持極高的光學局限因子 (Optical confinement factor)。

Fig. 2 (112.5 GBaud PAM4 傳輸測試): 團隊先用 1.1 um 寬度的 EML 進行基準測試。在 1311.6 nm 波長下,背對背 (Back-to-back) 的 TDECQ 為 1.43 dB,即使經過 10 公里單模光纖傳輸,TDECQ 也僅微增至 1.57 dB,證明了該晶片具備出色的基線傳輸能力。

Fig. 3 (台地寬度對眼圖的影響): 為了榨出更高頻寬,團隊將台地寬度從 1.1 um 進一步微縮至 0.8 um。物理意義上,這使靜電電容大幅下降了約 30%。反映在 155 GBaud PAM4 (0.8 Vpp 驅動) 的光學眼圖上,TDECQ 顯著從 3.3 dB 改善到了 2.4 dB。在不破壞波導結構強度的前提下,成功提升了晶片的本質頻寬。

第二階段:挑戰打線寄生電感與基板材料革命 (Fig. 4 - Fig. 15)

即便晶片再快,傳統的打線封裝仍是個拖油瓶。

Fig. 4 & Fig. 5 (寄生電感與打線長度的拉扯): Fig. 4 建立了 EML 在氮化鋁 (AlN) 次黏著基板上的等效電路模型,點出「第一條打線 (1st wire)」是高頻寄生電感的主要來源。Fig. 5 的模擬曲線殘酷地顯示,若打線長度 L 為 600 um,3 dB 頻寬會卡在 60 GHz;就算逼近物理極限縮短到 300 um,頻寬也頂多摸到 85 GHz,這離 400G/lane 所需的 100 GHz 還差得遠。

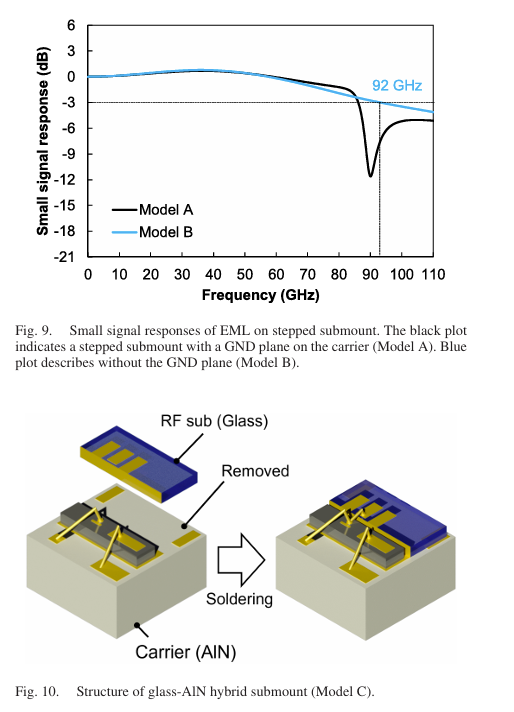

Fig. 6 - Fig. 9 (階梯式 AlN 基板設計與接地共振): 為了解決距離問題,Fig. 6 與 Fig. 7 (Model A) 提出使用兩塊 AlN 晶片組成「階梯式」基板,讓 RF 基板與 EML 等高,成功把打線長度縮到 100 um。然而,Fig. 9 的黑線模擬圖顯示,Model A 在 90 GHz 處出現了致命的訊號共振,這是因為 RF 基板背面的接地層產生了殘截線 (Stub) 效應。因此,Fig. 8 (Model B) 果斷去除了 RF 走線下方的接地層,成功消除了 90 GHz 的共振,將頻寬推升至 92 GHz (Fig. 9 藍線)。

Fig. 10 - Fig. 12 (Glass-AlN 混合基板的誕生): 92 GHz 還不夠!為了進一步利用低介電常數 (Low-Dk) 材料的優勢,團隊在 Fig. 10 (Model C) 換上了石英玻璃 (Quartz glass, 介電常數 3.8) 作為 RF 基板,並與具備優異散熱率及熱膨脹係數匹配的 AlN 載板結合。Fig. 11 模擬顯示此架構可將頻寬推上 106 GHz。Fig. 12 的實體剖面圖展示了厚度 100 um 的玻璃基板與 EML 緊密貼合的精湛工藝。

Fig. 13 & Fig. 14 (散熱與光學表現): 在 50°C 環境下,P-I 曲線 (Fig. 13) 沒有出現飽和或功率衰減 (Kink),光譜圖 (Fig. 14) 的邊模抑制比 (SMSR) 更超過 50 dB。這精準驗證了 AlN 底板完美扛下了熱負荷,確保了元件的長期可靠度。

Fig. 15 (混合基板小訊號實測): 迎來激動人心的實測結果!搭配 1.1 um 寬度的 EAM (電容約 60 fF),實測頻寬達到 100 GHz,與模擬高度吻合。當換上 0.8 um 寬度的極致 EAM (電容降至約 42 fF) 時,3 dB 頻寬直接衝破 110 GHz 的量測設備極限!這確立了 400G/lane 在打線架構下的可行性。

第三階段:面向 CPO/NPO 的去打線封裝技術 (Fig. 16 - Fig. 19)

為了迎合高邊緣密度 (High edge density) 的光電融合趨勢,傳統打線占用的面積已顯得奢侈。

Fig. 16 (高密度封裝概念): 展示了不需打線的 3D (Junction-up) 與 2.5D (Junction-down) EML 封裝架構,讓電子積體電路 (EIC) 與光子積體電路 (PIC) 能更緊密結合。

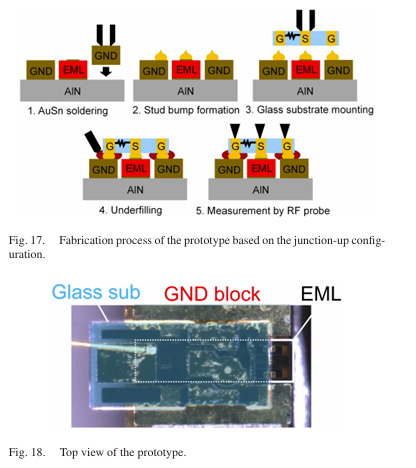

Fig. 17 & Fig. 18 (原型製作與俯視圖): 團隊實際試作了 Junction-up 架構 (Fig. 17)。為了讓 RF 玻璃基板能直接壓合,他們在 EML 兩側放置了等厚的接地塊 (GND blocks),並使用雙層金柱凸塊 (Au stud bumps) 來補償大約 10 um 的高度公差。Fig. 18 俯視圖呈現了這種將端接電阻與峰化電感單片整合在玻璃基板上的高整合度設計,間距設計更支援 500 um 的陣列擴展。

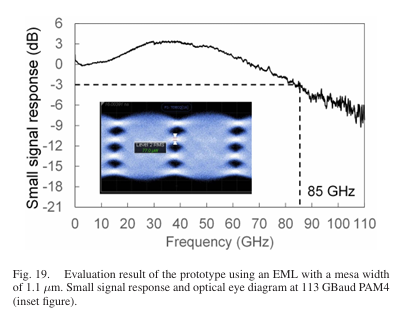

Fig. 19 (無打線封裝實測表現): 實測結果顯示 3 dB 頻寬達到 85 GHz。雖然因為訊號需穿透石英基板內的金屬通孔,加上雙層金柱凸塊帶來了額外的寄生電感,導致頻寬略低於 Fig. 15 的 100 GHz,但此架構仍成功跑出了 113.4 GBaud PAM4 的清晰眼圖 (1.0 Vpp 調變電壓下,TDECQ 估算為 1.8 dB,消光比 4.9 dB)。作者也務實地指出,未來透過擴大通孔直徑即可進一步收斂寄生電感、推升頻寬。

結論:產業的下一步

Mitsubishi Electric 的這篇論文不僅展現了深厚的 InP 磊晶與晶片設計底蘊,更在「高頻封裝」這個往往被低估的環節打出了漂亮的一擊。Glass-AlN 混合基板的商用化潛力極高,它讓現有的 3.2T 可插拔光模組能在確保散熱與可靠度的前提下,順利叩關 100 GHz 頻寬。而他們在無打線 CPO 封裝上的探索,更是為未來 AI 叢集內部超高密度光電共封裝鋪平了道路。從光通訊產業鏈的角度來看,這意味著高功率 EML 依然是 400G/lane 時代不可忽視的重磅玩家。

留言